Part Number: AM62L

Other Parts Discussed in Thread: UNIFLASH, , AM620-Q1, AM62P, SYSCONFIG, AM625, AM623, AM625-Q1, AM6421, SK-AM62B-P1, AM6442, AM2432, SK-AM62P-LP, AM2431, AM67A, SK-AM62A-LP, AM6548, AM62A3

Tool/software:

Hi TI Experts,

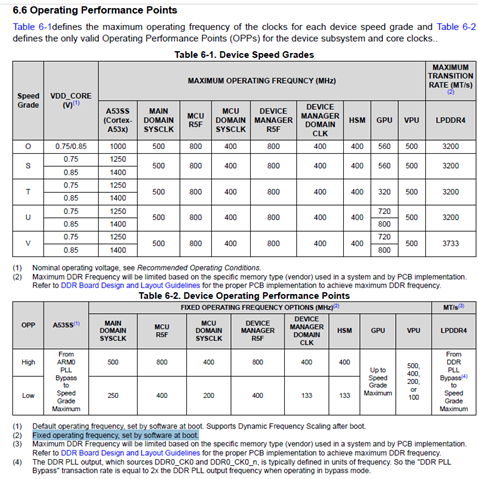

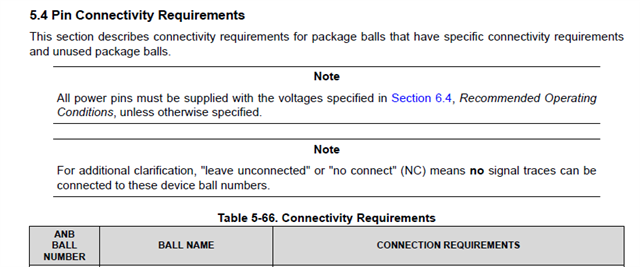

Please share your inputs on processor core, thermal alert, VDD_CORE, VDDR_CORE, VPP and other supplies

Please share any available information related to the cores that can be used during custom board design

Overview of key SoC subsystems ...

https://www.ti.com/video/series/indonesia-seminar.html

Overview of TI's embedded processing portfolio

https://www.ti.com/video/6378289827112

Note:

Application Report TDA4 Flashing Techniques

https://www.ti.com/lit/an/spracy5/spracy5.pdf

Benchmark

https://www.ti.com/lit/an/spradg0a/spradg0a.pdf

FAQ describing steps to use dfu to flash to eMMC:

[FAQ] SK-AM62: How to flash eMMC using USB DFU on AM62x-SK E2

To remove DDR dependency for UART UNIFLASH

RE: AM2431: AM2431 – UART Uniflash to OSPI Flashing Failure with HS-FS SBL on Custom Board

Suspend to Ram

Tweaking QoS and CoS Settings for DDR Bandwidth Optimization on TDA4x and AM6x Devices

https://www.ti.com/lit/an/sprads6/sprads6.pdf

(+) AM62A7: TIDSS Error - Processors forum - Processors - TI E2E support forums

They experience screen tearing on DSS in some DDR-heavy applications, which we mitigated by reducing A53 traffic priority. Their application is camera mirror system, so display latency / quality was important. We left other priorities as-is. I’m not sure what to recommend holistically for the device, but if I had to prioritize, I should think to have greater/default priority for CSI, VPAC/DMR5, C7x, and probably A53’s while reducing priority for other components.

The resolution used in that thread was to explicitly set MMR”s with these COS settings. The right way is probably to set these bits during a bootloader stage

AM275, AM62D, AM62A: Early CAN response