Hi Board designers,

Refer FAQs listed below related to custom board design for AM64x and AM243x processor families that could be used along with other available design collaterals:

Downloadable excel sheet for ease of use and better searchability: 3113.FAQs Master list_processor family wise.xlsx

To be able to quickly view and navigate all the published FAQs (including latest published FAQs) for all the TI processor families including custom board hardware design FAQs relevant to Sitara processor families (AM62x, AM62Ax, AM62Px, AM62D-Q1 and AM335x), a filter has been added.

The up-to-date published list of FAQs for all the TI processor families can be found at this link

To view the FAQs relevant to Sitara processor families released after the last sync, look for "custom board hardware design" phrase and published date in the listed FAQs. FAQs released before the sync date are are listed in the FAQ as a table. An excel that lists the FAQs published till the sync date is added for customers to download.

Last sync: 30th January 2025

Note: FAQs Highlighted with yellow color are generic and can be used for AM64x processor family

Regards,

Sreenivasa

Hi TI Experts,

I have the below queries on using the Ethernet interface peripherals in my design.

1.Peripherals Supporting Ethernet interface

2.Number of Ethernet interfaces supported by CPSW3G

3.Number of Instances and Ethernet interfaces supported by PRU_ICSSG

4.Are all 6 Ethernet interfaces supported by any of the AM64x family of devices

5.Does all the devices in the Family support the same number of Ethernet interfaces?

6.What PRU_ICSSG functionality is on each AM64x device

7.Any recommendation for using MDIO interfaces

8.Is AM64x affected by the MDIO Errata

9.Do you have recommendations on adding series resistors for RGMII interface

10.Are the above series resistor recommendations valid for MII or RMII interface

11.Is there any clock recommendations When using Ethernet interface

12.Recommendations for using External clock oscillator

13.IO levels supported for Ethernet interface

14.Is the RGMII internal delay supported by the processor and is the RGMII internal delay configurable

15.Can AM64x CPSW handle both 100BASE RMII for one port and 1000BASE RGMII for another port?

16. Can i interface 2 X RMII PHYs with the PHY configured as Master

17. Do you have interfacing recommendations for RMII interface

Let me know your thoughts.

Hi TI Experts,

I have the below queries on using the SERDES0 in my design.

1. Supported Interfaces

2. Implementation Reference for PCIe

3. Implementation Reference for USB3.0

4. Can i use PCIe and USB3.0 interface at the same time

5. Is AM64 able to change PCIE driving? If yes, how to do?

Let me know your thoughts.

Part Number: J721EXSOMXEVM

Using the 9.0 the U-Boot building if failing.

The building for R5 is ok, but failed for A72

//Setting the tool chain path

export PATH=xxx/ti-processor-sdk-linux-adas-j721e-evm-09_00_00_08/external-toolchain-dir/arm-gnu-toolchain-11.3.rel1-x86_64-arm-none-linux-gnueabihf/bin:$PATH

export PATH=xxx/ti-processor-sdk-linux-adas-j721e-evm-09_00_00_08/external-toolchain-dir/arm-gnu-toolchain-11.3.rel1-x86_64-aarch64-none-linux-gnu/bin:$PATH

//Compiling R5 and ARM64 images

cd xxx/ti-processor-sdk-linux-adas-j721e-evm-09_00_00_08/board-support

mkdir u-boot-build-output

cd u-boot-2023.04+gitAUTOINC+756ba776d4-g756ba776d4

//Several prebuilt images are required from the TI Processor SDK for building U-Boot on K3 based platforms.

//R5

make ARCH=arm CROSS_COMPILE=arm-none-linux-gnueabihf- j721e_evm_r5_defconfig O=xxx/ti-processor-sdk-linux-adas-j721e-evm-09_00_00_08/board-support/u-boot-build-output/r5

make ARCH=arm CROSS_COMPILE=arm-none-linux-gnueabihf- O=xxx/ti-processor-sdk-linux-adas-j721e-evm-09_00_00_08/board-support/u-boot-build-output/r5 BINMAN_INDIRS=/buildssd/mli1/wr1023-build-test/ti-processor-sdk-linux-adas-j721e-evm-09_00_00_08/board-support/prebuilt-images

//A72

make ARCH=arm CROSS_COMPILE=aarch64-none-linux-gnu- j721e_evm_a72_defconfig O=xxx/ti-processor-sdk-linux-adas-j721e-evm-09_00_00_08/board-support/u-boot-build-output/a72

make ARCH=arm CROSS_COMPILE=aarch64-none-linux-gnu- BL31=xxx/ti-processor-sdk-linux-adas-j721e-evm-09_00_00_08/board-support/prebuilt-images/bl31.bin TEE=xxx/ti-processor-sdk-linux-adas-j721e-evm-09_00_00_08/board-support/prebuilt-images/bl32.bin O=xxx/ti-processor-sdk-linux-adas-j721e-evm-09_00_00_08/board-support/u-boot-build-output/a72 BINMAN_INDIRS=xxx/ti-processor-sdk-linux-adas-j721e-evm-09_00_00_08/board-support/prebuilt-images

BINMAN .binman_stamp

binman: name 'ELFError' is not defined

Part Number: SK-AM62

I want to understand power and temperature relationships on the AM62A and/or the AM62X. How do I do this with the starter kit (SK) EVM?

Part Number: AM625

Hi

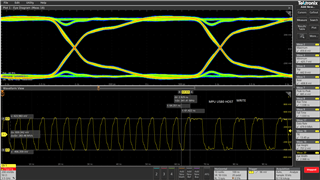

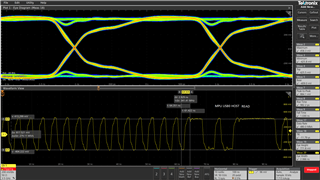

We are using AM625x in our design and we are performing DVT analysis of the USB interface on our board. We are observing the differential voltage exceeding 440mV. We are measuring 459.8 during write and 458.3mV during read which is slightly greater than the limit of 440mV. We are probing near the USB connector. Pls let us know if this is of any concern.

Regards

Prema

Part Number: AM6442

Hi TI Experts,

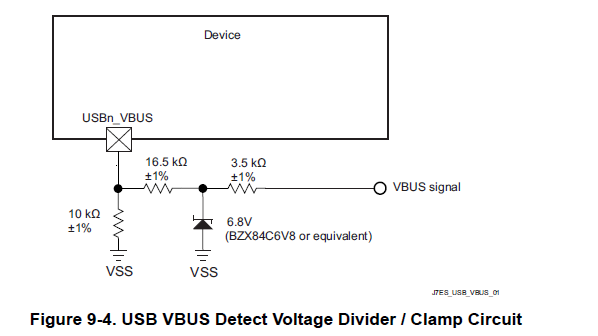

I have the below queries regarding implementation of USB interface

1. Supported USB interface configuration

2. Is VBUS connection required for Host configuration or Device configuration

3. Can I have the VBUS supply input connected when the SoC power supply is switched off

4. Is there a power sequencing requirement for VBUS

5. Can I connect 5V input from the USB connector directly to VBUS

6. Recommended VBUS supply voltage divider

7. SOC VBUS input voltage range and Zener diode connection

8. Supported USB Backup bootmode configuration.

9. Recommended USB RCALIB resistor

10. How to deal with the USB unused pins

11. Is the USB0_ID connection required for Host configuration or Device configuration.

12. Power supply switching and protection when the SOC is configured as USB Host

13. Are these recommendations valid for other Sitara processors or MCUs?

14. Do you have some recommendations on the Type-C implementation.

15. Can I use 3.4K instead of 3.5K.

16. Do the differential signal pins (USB, etc.) have the capabilities to adjust the swing of the voltage?

Let me know your thoughts.

Part Number: J784S4XEVM

None of the GPIO interrupts are firing on the 8.6 SDK of J784s4.

I am using an AM62Ax, AM62x, or AM64x device. My part number has fewer A53 cores than the maximum number of A53 cores in that part family (see below for specific part numbers). Or, my part number does NOT have a GPU core, in a part family that can have GPU cores (e.g., AM623x, AM620x).

During Linux boot, I am running into an error like this:

[ 17.491528] Internal error: synchronous external abort: 96000010 [#1] PREEMPT SMP [ 17.499023] Modules linked in: dwc3_am62(+) rti_wdt(+) virtio_rpmsg_bus ti_k3_m4_remoteproc snd_soc_tlv320aic26 sa2ul pruss sha512_generic authenc cdns_dphy ltc2945 at24 sch_fq_codel cryptodev(O) ipv6 [ 17.516894] CPU: 1 PID: 219 Comm: systemd-udevd Tainted: G O 5.10.168-yocto-standard #1 [ 17.526191] Hardware name: Critical Link MitySOM-AM62x (DT) [ 17.531760] pstate: 80000005 (Nzcv daif -PAN -UAO -TCO BTYPE=--) [ 17.537772] pc : rti_wdt_probe+0x1e8/0x4f0 [rti_wdt] [ 17.542738] lr : rti_wdt_probe+0x1d8/0x4f0 [rti_wdt] [ 17.547693] sp : ffff800011c5b920 [ 17.550999] x29: ffff800011c5b920 x28: 0000000000000100 [ 17.556309] x27: ffff80001011c1a8 x26: 0000000000000003 [ 17.561615] x25: ffff800011603d98 x24: 000000000000004a [ 17.566923] x23: ffff00000467a920 x22: ffff000002423400 [ 17.572231] x21: ffff00000467a890 x20: ffff000002423410 [ 17.577539] x19: ffff00000467a880 x18: 0000000000000000 [ 17.582848] x17: 0000000000000000 x16: 0000000000000000 [ 17.588155] x15: 0000000000000000 x14: ffff000005c0d580 [ 17.593463] x13: 0000000000000000 x12: ffff8000117dd000 [ 17.598769] x11: ffff8000117d7000 x10: 0000000000001000 [ 17.604078] x9 : ffff80001075c0fc x8 : ffff8000114c2b7c [ 17.609389] x7 : 0000000000000041 x6 : 000000000000008b [ 17.614697] x5 : 000000000e021000 x4 : ffff000002423610 [ 17.620005] x3 : ffff000005e5cd00 x2 : 0000000000000000 [ 17.625312] x1 : ffff000005c0b900 x0 : ffff8000117d5090 [ 17.630620] Call trace: [ 17.633071] rti_wdt_probe+0x1e8/0x4f0 [rti_wdt] [ 17.637691] platform_drv_probe+0x5c/0xb0 [ 17.641695] really_probe+0xf4/0x408 [ 17.645266] driver_probe_device+0x60/0xc0 [ 17.649357] device_driver_attach+0x7c/0x88 [ 17.653533] __driver_attach+0x70/0x100 [ 17.657362] bus_for_each_dev+0x78/0xc8 [ 17.661192] driver_attach+0x2c/0x38 [ 17.664762] bus_add_driver+0x15c/0x210 [ 17.668592] driver_register+0x6c/0x128 [ 17.672423] __platform_driver_register+0x50/0x60 [ 17.677124] rti_wdt_driver_init+0x2c/0x1000 [rti_wdt] [ 17.682260] do_one_initcall+0x4c/0x2e0 [ 17.686094] do_init_module+0x50/0x210 [ 17.689838] load_module+0x20fc/0x27a8 [ 17.693580] __do_sys_finit_module+0xb8/0xf8 [ 17.697843] __arm64_sys_finit_module+0x28/0x38 [ 17.702370] el0_svc_common.constprop.0+0x80/0x1d0 [ 17.707154] do_el0_svc+0x2c/0xa8 [ 17.710465] el0_svc+0x20/0x30 [ 17.713515] el0_sync_handler+0xb0/0xb8 [ 17.717343] el0_sync+0x180/0x1c0 [ 17.720659] Code: f9000260 b140041f 54001128 91024000 (b9400000) [ 17.726748] ---[ end trace fbd7824ab88012ad ]---

What is going on?

.

AM62Ax: the max number of A53 cores is 4, on AM62A*4. This FAQ applies to the other part numbers with 2 or 1 A53 cores: AM62A72, AM62A32, AM62A31

AM62x: the max number of A53 cores is 4, on AM62*4. This FAQ applies to the other part numbers with 2 or 1 A53 cores: AM6252, AM6251, AM6232, AM6231, AM6202, AM6201

AM64x: the max number of A53 cores is 2, on AM64*2. This FAQ applies to the other part numbers with 1 A53 core: AM6441, AM6421, AM6411

UPDATE January 2024: The information in this FAQ has been added to the processor academy modules. This FAQ will not be maintained going forward.

Please find the latest information in the processor's academy > Linux module > Porting > Porting CPU:

AM62x

AM62Ax

AM64x

Hi TI Experts,

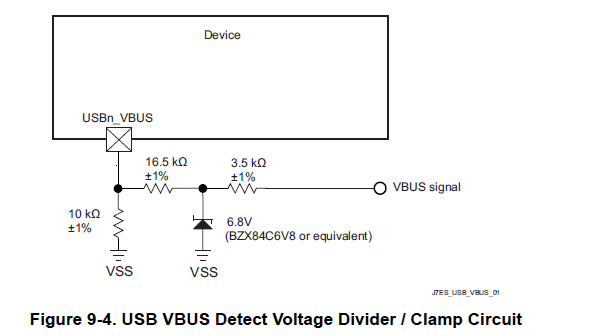

I have the below queries regarding implementation of USB interface

1. Supported USB interface configuration

2. Is VBUS connection required for Host configuration or Device configuration

3. Can i have the VBUS supply input connected when the SoC power supply is switched off

4. Is there a power sequencing requirement for VBUS

5. Can i connect 5V input from the USB connector directly to VBUS

6. Recommended VBUS supply voltage divider

7. SOC VBUS input voltage range and Zener diode connection

8. Supported USB Backup bootmode configuration.

9. Recommended USB RCALIB resistor

10. How to deal with the USB unused pins

11. Need details on the USBx_ID functionality

12. Power supply switching and protection when the SOC is configured as USB Host

13. Are these recommendations valid for other Sitara processors?

14. Do you have some recommendations on the Type-C implementation

15. Can i use 3.4K instead of 3.5K.

16. Do the differential signal pins (oLDI, USB, etc.) have the capabilities to adjust the swing of the voltage?

17. The End Equipment operates in slave mode when there are no USB equipment inserted. When a U disk (or other USB equipment) is inserted, it automatically switches to master mode. Could DRD mode achieve this function?

Let me know your thoughts.